Biography

I am a CPU Engineer at SiFive, working majorly on Physical Design & RTL Optimization. I have been a part of some really interesting projects here so far. Previously, I have worked for Google & Intel.

On the side of fun, I like to cook for friends & family. Ever so often, I also like to write poems at YourQuote. Like every music wannabe, I bought a keyboard recently and am sluggishly learning to play it. On weekends, I can be found in a quiet corner at some literary event in Bangalore.

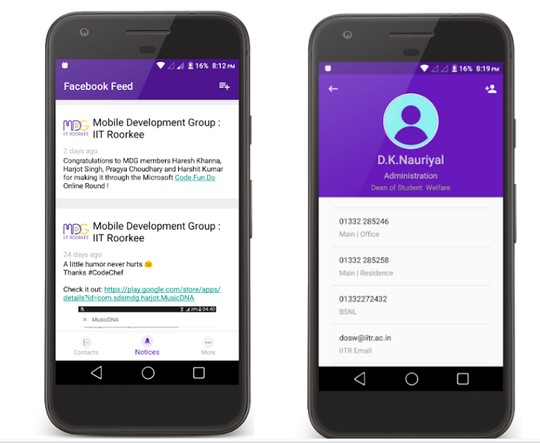

I graduated from IIT Roorkee in 2018, and have been in Bengaluru since then.

Interests

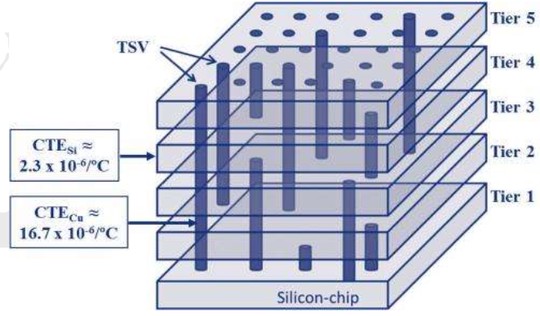

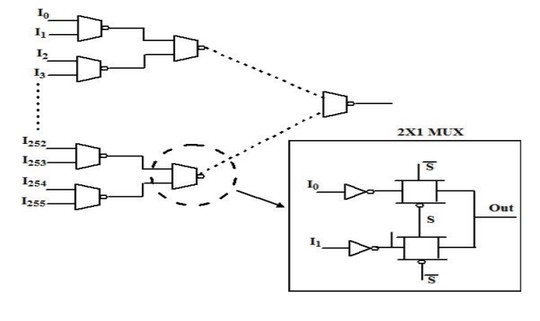

- VLSI Physical Design

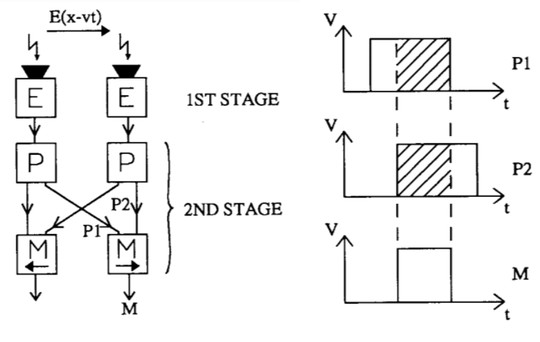

- Computer Architecture

- Device-Circuit co-design

- Delay Characterization

Education

-

Bachelor with Honors in Electronics and Communication, 2018

Indian Institute of Technology(IIT) Roorkee